The Challenge — Miniaturization vs. RF Integrity

In the race toward smaller, lighter, and more integrated microwave systems, engineers face an unavoidable trade-off: how to pack more functionality—LNAs, filters, phase shifters, power amplifiers—into limited PCB real estate without compromising signal integrity or dielectric stability.

Rogers Duroid 6010, with its high dielectric constant (Dk ≈ 10.2) and low loss tangent (Df = 0.0023 @ 10 GHz), enables dramatic miniaturization of RF circuits, but its dielectric sensitivity and thermal expansion mismatch introduce engineering challenges when combined with lower-Dk materials.

KKPCB’s hybrid stackup methodology bridges these gaps through multilayer dielectric engineering, controlled lamination, and via transition optimization, ensuring both mechanical stability and RF performance consistency up to 50 GHz.

Understanding the Stackup Problem

High-Dk Duroid 6010 layers reduce component size but concentrate electric fields within confined volumes. When combined with FR-4, RO4350B, or RO4003C cores, mismatched coefficients of thermal expansion (CTE) can cause layer warpage, microvia cracking, or impedance drift during thermal cycling.

| Challenge | Root Cause | RF/Mechanical Impact |

|---|---|---|

| Dielectric mismatch | Different Dk values (10.2 vs. 3.48) | Reflection & mode conversion |

| CTE mismatch | 12 ppm/°C (Duroid) vs. 17 ppm/°C (RO4003C) | Warpage, delamination risk |

| Copper imbalance | Uneven power-plane density | Bowing under reflow cycles |

| Via parasitics | Long z-axis transitions | Phase delay & resonance above 20 GHz |

KKPCB’s Hybrid Stackup Engineering Framework

1. Layer Function Segmentation

KKPCB separates signal, power, and ground layers across multiple dielectric systems:

-

Duroid 6010 for microwave and phase-critical traces

-

RO4003C for feed networks and low-loss transitions

-

FR-4 or low-Dk cores for DC and mechanical reinforcement

This approach ensures that only the high-frequency paths experience the Duroid environment, optimizing material usage while maintaining consistent phase velocity.

2. CTE-Balanced Lamination Control

-

Lamination pressure: 190 psi, temperature: 180 °C

-

Core alignment accuracy: < ±40 µm

-

Balanced copper across top and bottom planes prevents differential stress

3. Hybrid Bonding Interfaces

-

Low-flow PTFE prepregs ensure seamless bonding between Duroid 6010 and RO4003C.

-

Bond thickness control: ±8 µm to maintain impedance stability across interfaces.

4. Via and Transition Engineering

-

Back-drilled microvias reduce resonance up to 40 GHz.

-

Coaxial via barrels ensure uniform current distribution and controlled inductance.

-

3D EM simulation verifies smooth field transition between dielectric boundaries.

Duroid 6010 PCB

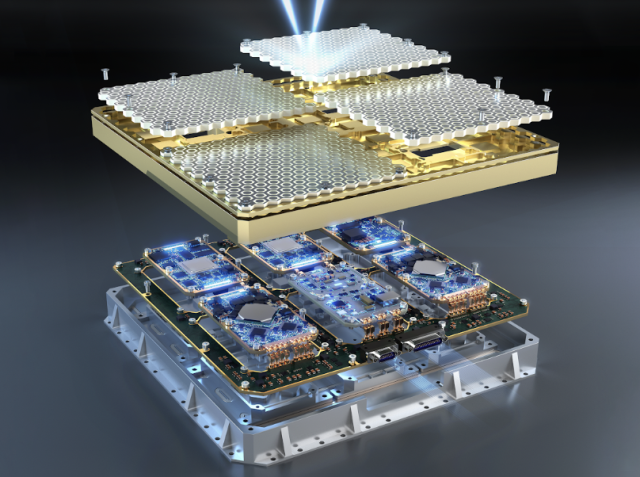

Case Study — X/Ku-Band Transceiver Packaging Module

Client: Southeast Asian defense electronics supplier

Objective: Miniaturize an X/Ku-band transceiver front-end (10–18 GHz) within a 3D multi-die RF package using hybrid dielectric integration.

Material Stackup:

-

Top RF layer: Duroid 6010 (0.254 mm)

-

Mid-frequency feed: RO4003C (0.2 mm)

-

Power distribution: FR-4 (0.3 mm)

-

Total thickness: 1.2 mm

Design Metrics:

| Target Parameter | KKPCB Result |

|---|---|

| Impedance tolerance | ±5 % |

| Insertion loss @ 18 GHz | 0.32 dB/inch |

| Phase skew | < 1.0° |

| Warpage (post-lamination) | < 0.08 mm / 200 mm panel |

Engineering Process Highlights:

-

Duroid 6010 RF paths routed on top microstrip layers with controlled impedance.

-

Differential mode filters embedded in RO4003C sub-layer.

-

Through-via transitions optimized with 3D coaxial shielding geometry.

-

Inline 40 GHz S-parameter validation to verify mode integrity.

Outcome:

KKPCB achieved a 30 % footprint reduction compared to a full-RO4003C design, while maintaining phase and amplitude stability over –55 °C to +125 °C cycles.

Advanced Design Considerations for RF Packaging

-

Power Integrity:

Hybrid copper redistribution layers (RDLs) minimize IR drop across multilayer boards. -

Thermal Flow:

Embedded copper coin and thermal via arrays dissipate localized hotspots in power amplifier regions. -

Resonance Control:

Layer-to-layer distance tuned to avoid λ/2 resonance cavity formation in stacked planes. -

Shielding:

Internal via fences and conformal EMI covers reduce radiation leakage by 12–15 dB.

These considerations are validated through EM co-simulation and thermal FEA, ensuring reliable packaging for mission-critical modules.

Environmental and Reliability Qualification

KKPCB subjects each hybrid Duroid 6010 stackup to a full qualification matrix:

| Test | Condition | Result |

|---|---|---|

| Thermal cycling | –55 °C ↔ +150 °C / 1000 cycles | No delamination |

| Humidity exposure | 85 °C / 85 % RH / 1000 h | Dk drift < 0.2 % |

| Reflow test | 260 °C × 3 cycles | Warpage < 0.08 mm |

| RF stability | 10–40 GHz | Insertion loss variation < 0.05 dB |

The results confirm structural stability and RF consistency across harsh military and industrial temperature ranges.

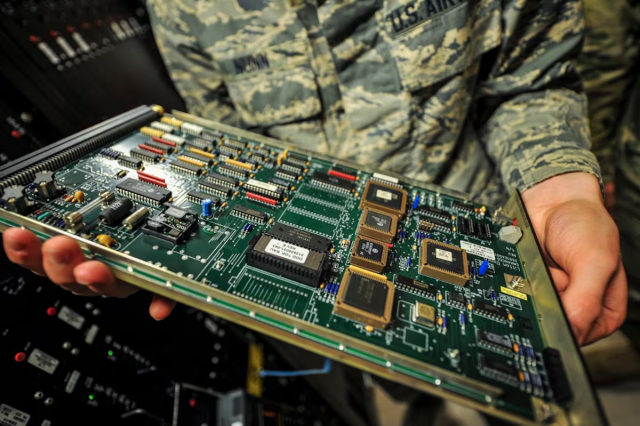

KKPCB Quality and Process Traceability

KKPCB’s hybrid Duroid 6010 PCB systems integrate:

-

Material batch Dk/Df verification under controlled humidity

-

Vacuum lamination with dielectric thickness calibration

-

110 GHz VNA and TDR validation for every prototype

-

Statistical process control (SPC) for impedance and CTE uniformity

Each board is manufactured under IPC-6018 and MIL-PRF-31032 standards, ensuring metrology-level precision for high-reliability RF and microwave packaging.

Conclusion — Engineering the Future of Compact RF Packaging

By leveraging Duroid 6010’s high-Dk precision and KKPCB’s hybrid stackup expertise, engineers can design denser, lighter, and more stable RF systems for defense radar, 5G infrastructure, and satellite communication modules.

-

Process-matched lamination and impedance tuning

-

Full environmental reliability testing and certification

Contact KKPCB Engineering to discuss your next-generation hybrid RF packaging project—where high-Dk precision meets real-world reliability.