Engineering Ultra-Low-Loss RF Path Consistency Through KKPCB’s Precision Manufacturing Framework

From Material Purity to mmWave Signal Integrity

As mmWave and phased array technologies push operational frequencies beyond 40–110 GHz, signal integrity becomes the decisive factor defining array accuracy, beam steering precision, and system reliability.

Rogers Duroid 5880, known for its ultra-low dielectric loss (Df = 0.0009 @ 10 GHz) and stable Dk = 2.20 ± 0.02, enables extremely low dispersion and minimal phase delay variation across wide frequency bands.

However, ensuring these material properties translate into repeatable electrical performance requires tightly controlled PCB manufacturing, surface uniformity, and connector transition engineering—especially for dense antenna arrays and calibration networks.

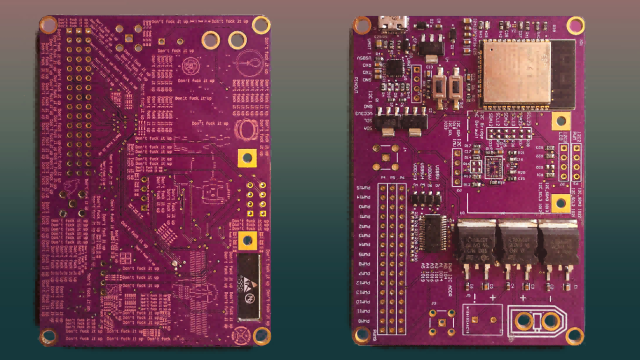

KKPCB’s precision RF manufacturing process transforms Duroid 5880’s intrinsic electrical potential into consistent high-frequency signal integrity suitable for phased array, radar, and satellite communication modules.

Why Signal Integrity Defines mmWave Antenna Reliability

In antenna arrays operating from 28 GHz to 110 GHz, even minute impedance or loss deviations can cause cumulative phase misalignment:

| Challenge | Root Cause | System-Level Impact |

|---|---|---|

| Insertion Loss Variability | Copper roughness, laminate moisture absorption | Uneven amplitude distribution across array channels |

| Impedance Drift | Dielectric thickness fluctuation or resin flow instability | Beam skew and degraded radiation efficiency |

| Phase Instability | Uneven substrate expansion (CTE > 15 ppm/°C) | Beamforming error and calibration drift |

| Connector Transition Loss | Incomplete ground return, plating thickness variation | Increased reflection (S11 > –15 dB) |

KKPCB mitigates these errors through advanced lamination balance, surface planarization, and inline 110 GHz impedance verification.

KKPCB’s Engineering Framework for Signal Integrity Control

1. Dielectric Uniformity and Moisture Control

-

Pre-bake Duroid 5880 laminates at 120 °C / 4 h to eliminate micro-moisture.

-

Vacuum lamination with dielectric thickness tolerance ± 8 µm.

-

Dk drift < ± 0.01 across 10–110 GHz bandwidth verified by VNA.

2. Surface Conductor Optimization

-

Rolled annealed (RA) copper with Ra < 0.8 µm reduces insertion loss variation to < 0.05 dB/inch.

-

Controlled etch process (± 5 µm precision) ensures uniform microstrip impedance.

3. Connector and Launch Transition Engineering

-

Embedded coaxial via transitions simulated through 3D EM modeling (HFSS).

-

Controlled plating (15–18 µm Cu + 1.5 µm Ni/Au) ensures reflection < –20 dB.

4. Thermal Stress and Phase Consistency Testing

-

Thermal cycling: –55 °C ↔ +150 °C / 1000 cycles.

-

Phase shift measured < 1° @ 77 GHz across 250 mm trace.

Case Study — 94 GHz Airborne Phased Array Receiver Module

Client: Aerospace radar integrator specializing in synthetic aperture radar (SAR).

Objective: Achieve amplitude deviation < 0.1 dB and phase error < 1° across 256 array elements.

Challenges Identified:

-

Thin (0.254 mm) Duroid 5880 core with high panel warpage under multilayer bonding.

-

Uneven dielectric compression leading to 6 % impedance variance.

-

Dual-layer 5880 + PTFE low-flow bonding film for matched CTE (< 12 ppm/°C).

-

Controlled lamination: 175 °C / 65 min / 180 psi with slow cooling gradient.

-

Inline S-parameter validation at 90 GHz for every panel.

| Parameter | Before Optimization | After KKPCB Process |

|---|---|---|

| Insertion Loss | 0.32 dB/inch | 0.24 dB/inch |

| Phase Error | 2.1° | 0.8° |

| Panel Warpage | 0.23 mm / 250 mm | 0.09 mm / 250 mm |

| Yield Rate | 87 % | 98.6 % |

Outcome:

The array achieved beam steering accuracy < 0.5°, meeting MIL-STD thermal reliability with no delamination or drift after 1000 thermal cycles.

Design & Process Best Practices

-

Maintain symmetrical dielectric balance to reduce phase skew.

-

Use PTFE-based low-flow bonding films (CTE-matched to 5880).

-

Limit lamination cycles < 2 to preserve Dk stability.

-

Perform full-band impedance scan (1–110 GHz) before final assembly.

-

Validate connector planarity to avoid ground discontinuity at launch.

KKPCB’s RF Quality & Reliability Framework

-

Inline VNA calibration up to 110 GHz with NIST-traceable reference.

-

3D lamination simulation for CTE and thermal flatness control.

-

Accelerated aging test: 85 °C / 85 % RH / 1000 h → Df drift < 0.0001.

-

IPC Class 3 / IATF 16949 compliance for aerospace-grade reliability.

Conclusion — Turning Duroid 5880’s Material Precision into System-Level Accuracy

Duroid 5880 enables exceptional low-loss and phase-stable designs—but without precise manufacturing control, its performance advantages can diminish rapidly at mmWave frequencies.

KKPCB’s engineered process converts Duroid 5880’s intrinsic dielectric stability into measurable system benefits:

-

< 1° phase variation across 90 GHz channels.

-

Stable impedance ± 5 % across hybrid stackups.

-

Consistent array alignment under thermal and mechanical stress.

From prototype validation to scalable phased array production, KKPCB ensures signal integrity, reliability, and calibration stability for next-generation mmWave systems.